# 16-bit 125MSPS dual-channel Analog-to-Digital Converter (ADC)

### 1 Main features:

- Conversion bits: 16 bits

- Clock frequency: 125 MSPS

- Supply voltage: 1.8V

- Power consumption: 375 mW/CH

- Data interface: CMOS/LVDS interface

- SFDR: 88dBc@70MHz input

- SNR: 78.7dBFS@70MHz i nput

- ♦ Optional in-film jitter

- Programmable ADC internal reference voltage source

- 1 to 8 integer input clock divider

- Encapsulation: QFN64

### 2. Typical applications

- Wireless communication system

- Intelligent antenna system

- 🔶 Software radio

- Broadband data application

- Medical ultrasound equipment

- Radar and aviation systems

#### **3 Product Description**

5

The chip is a 16-bit, 125 MSPS dual-channel ADC designed for communication applications requiring high performance, low cost, and small size. The ADC core uses a multi-level, differential pipeline architecture and integrates output error correction logic. The front-end wideband differential sampling and holding circuit allows users to flexibly select various input ranges. The reference voltage circuit is integrated in the chip.

Compared with similar foreign products

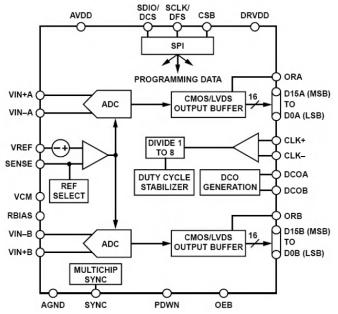

The chip has a clock duty ratio regulator, which can compensate the fluctuation of ADC clock duty ratio and ensure the output performance of the converter. The output of the chip is CMOS signal or LVDS signal. The chip has a power saving mode to reduce power consumption. The chip implements various configurations through the three-wire SPI interface. The chip adopts QFN64 package, which is compatible with foreign products AD9268 pin and can be replaced. The internal structure block diagram of the chip is as follows:

## 4 Product Highlights

• Optional on-chip jitter option improves smallsignal SFDR performance.

- Proprietary differential inputs maintain excellent

- SNR at 300 MHz input frequencies.

Standard serial port configuration: output data

format, clock DCS enable, power saving mode, test mode,

reference voltage value, etc.

|         | precision | Clock<br>frequency | Data port | Power dissipation | SNR       | SFDR         | Encapsulation<br>form |

|---------|-----------|--------------------|-----------|-------------------|-----------|--------------|-----------------------|

| AD9268  | 16Bit     | 125MHz             | CMOS/LVDS | 750mW@25          | 78.2dBFS@ | 88dBc@70 MHz | LFCSP64               |

| (ADI)   |           |                    |           | 0MSPS             | 70MHz     |              |                       |

| ADS6445 | 14Bit     | 125MSPS            | LVDS      | 420mW@            | 72.7dBFS@ | 78dBc@70 MHz | QFN64                 |

| (TI)    |           |                    |           | 125MSPS           | 70MHz     |              |                       |

| HL9268  | 16Bit     | 125MHz             | CMOS/LVDS | 750mW@1           | 78.7dBFS@ | 88dBc@70 MHz | QFN64                 |

|         |           |                    |           | 25MSPS            | 70MHz     |              |                       |