# Introduction

This migration guide is designed to help you analyze the steps required to migrate from an existing SXX32F103 device to an MH2103C device. This document gathers the most important information and lists the important things to be aware of.

To port an application from the SXX32F103 series to the MH2103C series, users need to analyze hardware migration, peripheral migration, and firmware migration.

Supported model list:

Supported model MH2103Cxxxx

# Catal ogue

| 1.  | Quickly replace the SXX32F103 chip4                                                              |

|-----|--------------------------------------------------------------------------------------------------|

| 2.  | Precautions for hardware migration5                                                              |

| 2   | .1 GPIO pin voltage withstand description5                                                       |

| 2   | .2 USB pin instructions5                                                                         |

| 2.3 | Bootstrap mode select pin5                                                                       |

| 3.  | Precautions for software migration6                                                              |

| 3.1 | System module6                                                                                   |

|     | 3.1.1 Interrupt controller precautions                                                           |

|     | 3.1.2 Bootstrap mode configuration options are not reloaded during soft reset                    |

|     | 3.1.3 Non-32bit alignment access APB bus precautions6                                            |

|     | 3.1.4 Precautions to distinguish the MH2103C chip from the SXX32F103 chip7                       |

|     | 3.1.5 Software delay precautions8                                                                |

|     | 3.1.6 TRACESWO as a Printf function                                                              |

| 3   | . 2 ADC module                                                                                   |

|     | 3.2.1 The ADC is configured to trigger continuously. Precautions for stopping the trigger9       |

|     | 3.2.2 Software trigger Precautions for enabling ADON to perform external events twice in a row10 |

|     | 3.2.3 Software trigger Precautions for enabling ADON to perform external events twice in a row11 |

|     | 3.2.4 Precautions for using different modes of dual ADC11                                        |

|     | 3.2.5 Precautions for ADC and DMA configuration12                                                |

|     | 3. 2. 6 ADC automatic injection mode use precautions13                                           |

| 3   | .3 TIM module13                                                                                  |

|     | 3.3.1 Precautions for using external brakes13                                                    |

|     | 3. 3. 2 Precautions for software CNT value modification14                                        |

| 3   | . 3. 3 Precautions for using the TIM DMA Burst function15                                        |

| 3   | 16 A CAN module                                                                                  |

|     | 3.4.1 Precautions for configuring a filter in hibernation mode16                                 |

|     | 3.4.2 Send time stamp precautions16                                                              |

| 3   | . 4.3 When TXFP is 1, the FIFO priority is different                                             |

| 3   | . 5 FLASH module20                                                                               |

| 3   | .5.1 Precautions for invoking the FLASH_EraseOptionBytes() interface20                           |

| 3   | . 6 USART module23                                                                               |

### Port from SXX32F103 to MH2103C

| 3.6.1 Precautions for clock output in smart card mode23                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.6.2 Using DMA to send data, check whether all data is sent through<br>the USART TC flag. Precautions24<br>3.6.3 Smart card & Single-wire half-duplex mode TX pin configuration precautions26 |

| 3.6.4 Precautions for DR Overflow when accepting data26                                                                                                                                        |

| 3.7 SPI module                                                                                                                                                                                 |

| 3.7.1 As the Master, this section describes the precautions for sending and receiving data in full-duplex mode                                                                                 |

| 3.7.2 Turn off the SPE in BUSY state                                                                                                                                                           |

| 3.7.3 Precautions for data transmission using DMA                                                                                                                                              |

| 3.8 USB module                                                                                                                                                                                 |

| 3.8.1 USB use precautions29                                                                                                                                                                    |

| 3.9 DMA module                                                                                                                                                                                 |

| 3.9.1 DMA usage precautions                                                                                                                                                                    |

| 3.10 IIC module                                                                                                                                                                                |

| 3.10.1 Send start bit & Stop bit as Master Note                                                                                                                                                |

| 4. ISP, emulator, offline burner use precautions                                                                                                                                               |

| 4.1 ISP tool usage Precautions                                                                                                                                                                 |

| 4.2 Precautions for using emulator                                                                                                                                                             |

| 4.2.1 Precautions for using Keil.SXX32F1xx_DFP.2.3.0 or later pack33                                                                                                                           |

| 4.3 Notes on the use of downloader                                                                                                                                                             |

| 4.3.1 When the chip is in the read/write protection state, burn precautions35                                                                                                                  |

| 4.3.2 Precautions for using WizPro200ST8 programmer                                                                                                                                            |

| Historical version                                                                                                                                                                             |

The MH2103C series microcontrollers are basically compatible with the SXX32F103

series, while enhancing many features, with some differences from the

SXX32F103, detailed in this document.

# 1. Quickly replace the SXX32F103 chip

•Step 1: Compare peripheral specifications, Flash capacity, SRAM capacity, etc. , unsolder SXX32F103 and replace it with the corresponding model of MH2103C

•Step 2: Use ISP or KEIL to download the SXX32F103 HEX file or BIN file.

•Step 3: Download data other than SXX32F103 HEX file or BIN file or perform system corrections if necessary.

•Step 4: Check whether the program works properly.

•Step 5: Quick troubleshooting of other problems please refer to  $2\3$  electrical  $\$  software transplantation precautions.

•Step 6: If the program does not work properly after the above steps, please refer to the other sections of this document, or contact the distributor and MH support staff for assistance.

# 2. Precautions for hardware migration

# 2.1 GPIO pin voltage withstand description

MH2103C PA11, PA12 pin withstand voltage limit is 3.6V, hardware

circuit design pay attention to the voltage range.

Note:

The optional multiplexing functions of PA11 pin are CAN\_RX, USART1\_CTS, USBDM, TIM1\_CH4;

The optional multiplexing functions of PA12 pin are CAN\_TX, USART1\_RTS, USBDP, TIM1\_ETR;

# 2.2 USB pin instructions

When MH2103C uses USB, it is recommended to protect PA11 and PA12

with TVS diode.

# 2.3 Bootstrap mode select pin

When the BOOTO pin is suspended, the chip has a probability of starting the execution program from the non-flash area after the reset startup. If you need to boot from user Flash, avoid dangling BOOTO.

An external 10K pull-down resistor or direct ground is recommended for BOOTO pins, Can stably boot from user Flash.

| Bootstra<br>select p | p mode | Bootstrap mode | Aliasing                                        |

|----------------------|--------|----------------|-------------------------------------------------|

| BOOT1                | BOOTO  | bootstrap mode | Arrastny                                        |

| Х                    | 0      | User Flash     | Select user Flash as the bootstrap space        |

| 0                    | 1      | System memory  | Select system memory as the bootstrap space     |

| 1                    | 1      | Embedded SRAM  | Select the embedded SRAM as the bootstrap space |

# 3. Precautions for software migration

# 3.1 System module

# 3.1.1 Interrupt controller precautions

- > Supports a maximum of 71 masked interrupt channels.

- > Eight programmable priority levels (using a 3-bit interrupt priority).

# 3.1.2 Bootstrap mode configuration options are not reloaded during soft reset

# Example of exceptions (Enabling read/write protection through an ISP) :

- $\succ$  B00TO connects to high, B00T1 connects to low, external Reset, successfully connects to ISP.

- Set BOOTO to low and enable read/write protection through ISP.

After read/write protection is enabled, programs in the Flash are not executed.

# Root cause:

After read/write protection is enabled through the ISP, the chip automatically initiates a system reset. During soft reset, the boot-up configuration pin is not reloaded and the BOOT pin configuration status is maintained. Therefore, the program is executed in the system memory again, resulting in no program execution in the Flash.

# Sol ution:

After the bootstrap mode is changed, you can RESET the chip through

external reset or power it on or off again.

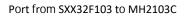

# 3.1.3 Non-32bit alignment access APB bus precautions

# Problem description:

When the ADC is configured in left-justified mode, the converted high 8bit data is obtained from the address 0x4001244E, and the obtained value is

# fixed to O.

The program is configured as follows:

### Root cause:

When accessing the APB bus, you must use 32-bit alignment; otherwise, the APB bus cannot be accessed.

Sol uti on:

When accessing the registers of the APB bus, the alignment needs to be 32bit. If you need a field in the 32bit register, read it out in alignment and then process it.

### 3.1.4 Precautions to distinguish the MH2103C chip from the SXX32F103 chip

Read the base address 0x1FFF7E8 and get a 32bit identifier to distinguish. As shown in the picture below: The identification is described as follows:

| Model number | Type identification |

|--------------|---------------------|

| MH2103C CBT6 | 0x1C5A5BBX          |

| MH2103C CCT6 | 0x1C5A5CCX          |

# 3.1.5 Software delay precautions

# Problem description:

Some software delays implemented using other platforms need to be adjusted, such as the following simple software delay function:

The delay time for SXX32F103 to execute this function is 10us.

The delay time for MH2103C to execute this function is 7.2us.

If the application has strict requirements on the software delay time

, adjust the software delay parameters to some extent

# 3.1.6 TRACESWO as a Printf function

# Problem description:

When TRACESWO pin (PB3) is used as the Log output, no Log is found.

# Root cause:

MH2103CPB3 takes precedence over TRACESWO as a JTDO function.

# Solution:

If TRACESWO pins (PB3) are used as Log output, JTAG multiplexing needs to be configured.

As shown below:

RCC\_APB2PeriphClockCmd(RCC\_APB2Periph\_AFIO,ENABLE);

GPIO\_PinRemapConfig(GPIO\_Remap\_SWJ\_JTAGDisable,ENABLE);

# 3.2 ADC module

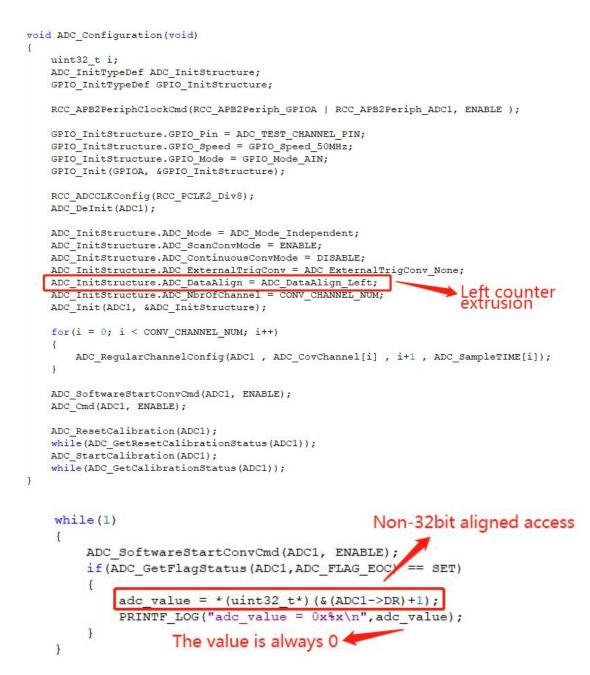

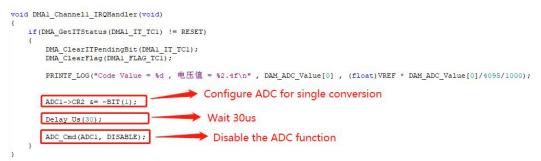

# 3.2.1 The ADC is configured to trigger continuously. Precautions for stopping

# the trigger

Repeat the problem as follows:

- Configure ADC for continuous sampling and enable DMA handling. After the software is triggered, ADC conversion completes once, DMA handling completes once, and DMA completion interrupts once.

- Configure to turn off ADC enablement in DMA completion interrupt.

MH2103C will continue to convert the ADC after disabling the ADC, and  $\triangleright$  will continue to enter the DMA completion interrupt

| oid ADC_Configuration(void)                    |                            |                                   |

|------------------------------------------------|----------------------------|-----------------------------------|

| uint32 t i;                                    |                            |                                   |

| ADC InitTypeDef ADC InitStructure              | e;                         |                                   |

| GPIO_InitTypeDef GPIO_InitStruct               |                            |                                   |

| RCC_APB2PeriphClockCmd(RCC_APB2P               | eriph_GPIOA   RCC_APB2Peri | ph_ADC1, ENABLE );                |

| GPIO_InitStructure.GPIO_Pin = AD               | C_TEST_CHANNEL_PIN;        |                                   |

| GPIO InitStructure.GPIO Speed = 0              | GPIO Speed 50MHz;          |                                   |

| GPIO InitStructure.GPIO Mode = G               | PIO Mode AIN;              |                                   |

| GPIO_Init(GPIOA, &GPIO_InitStruc               | ture);                     |                                   |

| RCC_ADCCLKConfig(RCC_PCLK2_Div8)               | ;                          |                                   |

| ADC_DeInit(ADC1);                              |                            |                                   |

| ADC InitStructure.ADC Mode = ADC               | Mode Independent;          | The function is set to trigger    |

| ADC InitStructure.ADC ScanConvMo               |                            | continuously                      |

| ADC InitStructure.ADC Continuous               |                            |                                   |

| ADC InitStructure.ADC ExternalTr.              | igConv = ADC ExternalTrigC | onv None;                         |

| ADC InitStructure.ADC DataAlign                | = ADC DataAlign Right;     | 5 Th                              |

| ADC InitStructure.ADC NbrOfChann               | el = CONV CHANNEL NUM;     |                                   |

| ADC_Init(ADC1, &ADC_InitStructur               | e);                        |                                   |

| <pre>for(i = 0; i &lt; CONV CHANNEL NUM;</pre> | i++)                       |                                   |

|                                                |                            |                                   |

| ADC RegularChannelConfig(ADC                   | 1 , ADC CovChannel[i] , i+ | 1 , ADC SampleTIME[i]);           |

| }                                              |                            | transport. Once the conversion is |

|                                                | complete DMA               | transport is performed once.      |

| DMA Configuration();                           | complete, DIVIA            | transport is performed once.      |

|                                                |                            |                                   |

| ADC Cmd(ADC1, ENABLE);                         | Enabling ADC               |                                   |

| ADC ResetCalibration(ADC1);                    |                            |                                   |

| while (ADC GetResetCalibrationSta              | tus(ADC1));                |                                   |

| ADC StartCalibration (ADC1);                   |                            |                                   |

| while (ADC_GetCalibrationStatus (A             | DC1));                     |                                   |

|                                                | Cof                        | tware trigger                     |

| ADC SoftwareStartConvCmd(ADC1, E               | NABLE); SOI                | tware trigger                     |

# Solution:

Configure ADC for single conversion and wait until the last sampling period is ADC\_CLK before disabling ADC.

As shown in the picture below:

The ADC clock configured in the above example is 9M and the sampling period is 239.5.

Therefore, the waiting time is  $(239.5+12.5)*1/9000 \approx 27.922$ us, so the waiting time of 30us in the figure below is sufficient.

3.2.2 Software trigger Precautions for enabling ADON to perform external events twice in a row

#### Problem description:

After the above operation, MH2103C will fail to clear O after EOC setting, and abnormal ADC conversion value will occur.

# Sol uti on:

After enabling ADC, enable ADC again, wait for EOC to be set, and read the quantized value.

```

As shown in the picture below:

ADC_Cmd(ADC1, ENABLE);

ADC_Cmd(ADC1, ENABLE);

while(ADC_GetFlagStatus(ADC1,ADC_FLAG_EOC) == RESET);

ADC_GetConversionValue(ADC1);

ADC_SoftwareStartConvCmd(ADC1, ENABLE);

```

Attention:

When the ADC is enabled and the ADC is enabled again, both SXX32F103 and

MH2103C trigger an ADC conversion.

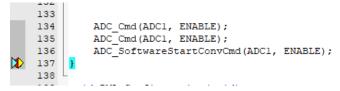

3.2.3 The ADC enables software triggers for external events twice in a row Problem description:

|                  | 133 |   | The software triggered two consecutive  |

|------------------|-----|---|-----------------------------------------|

|                  | 134 |   | ADC Cmd (ADC1, ENABLE); external events |

|                  | 135 |   |                                         |

|                  | 136 |   | ADC SoftwareStartConvCmd(ADC1, ENABLE); |

| $\triangleright$ | 137 |   | ADC SoftwareStartConvCmd(ADC1, ENABLE); |

| •                | 138 | } |                                         |

After the above operation, MH2103C will fail to clear 0 after EOC setting, and abnormal ADC conversion value will occur.

# Solution:

The software triggers the external event, waits for the EOC to set, and reads the quantized value.

As shown in the picture below:

```

ADC_SoftwareStartConvCmd(ADC1, ENABLE);

while(ADC_GetFlagStatus(ADC1,ADC_FLAG_EOC) == RESET);

ADC_GetConversionValue(ADC1);

ADC_SoftwareStartConvCmd(ADC1, ENABLE);

while(ADC_GetFlagStatus(ADC1,ADC_FLAG_EOC) == RESET);

ADC_GetConversionValue(ADC1);

```

3.2.4 Precautions for using different modes of dual ADC

Synchronous injection, alternate trigger mode:

SXX32F103: After the injection group channel or rule group channel is triggered , the conversion is normal. MH2103C: Normal transformation after the injection group channel is triggered; After the rule group channel is triggered, no conversion is performed.

Synchronous regular, fast crossover, slow crossover mode:

SXX32F103: After the injection group channel or rule group channel is triggered, the conversion is normal.

MH2103C: Normal transformation after the rule group channel is triggered; After the injection group channel is triggered, no conversion is performed.

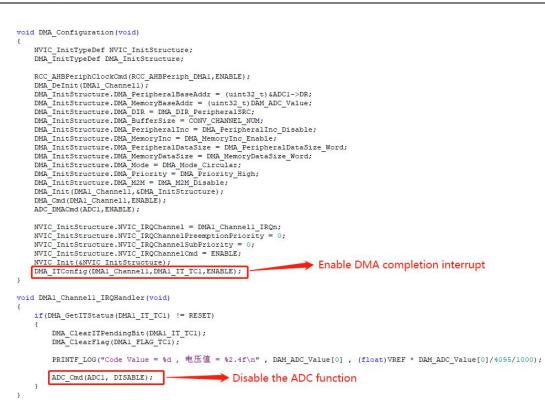

# 3.2.5 Precautions for ADC and DMA configuration

### Problem description:

When an ADC is configured to continuously sample multiple channels and DMA is used to move data, errors (mismatches) occur in ADC quantization values. For example, convert five channels, configure them as rule groups, and scan continuously for conversion.

Expectations for {0V,1V,1.5V,2V,2.5V, 0V,1V,1.5V,2V,2.5V, 0V,1V,1.5V,2V,2.5V ...};

To obtain the value of the actual software {1.5V,2V,2,5V,0V,1V, 1.5V,2V,2,5V,0V,1V, 1.5V,2V,2,5V,0V,1V ...}

The following figure shows the configuration

```

void ADC_Configuration(void)

uint32 t i;

ADC_InitTypeDef ADC_InitStructure;

GPIO_InitTypeDef GPIO_InitStructure;

RCC APB2PeriphClockCmd(RCC APB2Periph GPIOA | RCC APB2Periph ADC1, ENABLE );

GPIO InitStructure.GPIO Pin = ADC TEST CHANNEL PIN;

GPIO InitStructure.GPIO Speed = GPIO Speed 50MHz;

GPIO InitStructure.GPIO Mode = GPIO Mode AIN;

GPIO Init (GPIOA, &GPIO InitStructure);

RCC ADCCLKConfig(RCC PCLK2 Div8);

ADC DeInit(ADC1);

ADC_InitStructure.ADC_Mode = ADC_Mode_Independent;

ADC_InitStructure.ADC_ScanConvMode = ENABLE;

ADC_InitStructure.ADC_ContinuousConvMode = ENABLE;

ADC

InitStructure.ADC ExternalTrigConv = ADC ExternalTrigConv None;

ADC_InitStructure.ADC_DataAlign = ADC_DataAlign_Right;

ADC InitStructure.ADC NbrOfChannel = CONV_CHANNEL_NUM;

ADC_Init(ADC1, &ADC_InitStructure);

5 channels

for(i = 0; i < CONV CHANNEL NUM: i++)</pre>

{

ADC RegularChannelConfig(ADC1 , ADC CovChannel[i] , i+1 , ADC SampleTIME[i]);

¥

ADC ResetCalibration(ADC1):

while (ADC GetResetCalibrationStatus (ADC1));

ADC StartCalibration(ADC1);

while(ADC_GetCalibrationStatus(ADC1));

Enabling ADC and configuring

ADC_Cmd(ADC1, ENABLE);

DMA directly have other

instructions

// There are other directives function();

DMA Configuration();

}

```

### Sol ution:

If DMA is configured and then ADC is enabled, ADC quantization value error

(misalignment) does not occur.

As shown in the following picture

```

void ADC Configuration (void)

uint32 t i:

ADC InitTypeDef ADC InitStructure;

GPIO InitTypeDef GPIO InitStructure;

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA | RCC_APB2Periph_ADC1, ENABLE );

GPIO_InitStructure.GPIO_Pin = ADC_TEST_CHANNEL_PIN;

GPIO InitStructure.GPIO Speed = GPIO Speed 50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AIN;

GPIO Init (GPIOA, &GPIO InitStructure);

RCC ADCCLKConfig(RCC_PCLK2_Div8);

ADC_DeInit(ADC1);

ADC_InitStructure.ADC_Mode = ADC_Mode_Independent;

ADC_InitStructure.ADC_ScanConvMode = ENABLE;

ADC_InitStructure.ADC_ContinuousConvMode = ENABLE;

ADC

InitStructure.ADC_ExternalTrigConv = ADC_ExternalTrigConv_None;

ADC_InitStructure.ADC_DataAlign = ADC_DataAlign_Right;

ADC_InitStructure.ADC_NbrOfChannel = CONV_CHANNEL_NUM;

ADC Init(ADC1, &ADC InitStructure);

for(i = 0; i < CONV_CHANNEL_NUM; i++)</pre>

Ł

ADC_RegularChannelConfig(ADC1 , ADC_CovChannel[i] , i+1 , ADC_SampleTIME[i]);

1

ADC_ResetCalibration(ADC1);

while(ADC_GetResetCalibrationStatus(ADC1));

ADC StartCalibration(ADC1);

while (ADC_GetCalibrationStatus (ADC1));

DMA Configuration();

ADC Cmd(ADC1, ENABLE);

3

```

### 3.2.6 ADC automatic injection mode use precautions

When using ADC auto-injection mode, scanning needs to be enabled, as follows:

```

ADC_DeInit(ADC1);

ADC_InitStructure.ADC_Mode = ADC_Mode_Independent;

ADC_InitStructure.ADC_ScanConvMode = ENABLE;

ADC_InitStructure.ADC_ContinuousConvMode = DISABLE;

ADC_InitStructure.ADC_ExternalTrigConv = ADC_ExternalTrigConv_None;

ADC_InitStructure.ADC_DataAlign = ADC_DataAlign_Right;

ADC_InitStructure.ADC_NbrOfChannel = 2;

ADC_Init(ADC1, &ADC_InitStructure);

```

# 3.3 TIM module

### 3.3.1 Precautions for using external brakes

### Problem description:

When the time interval between two consecutive brakes is less than one TIM clock cycle, there will be a BIF(brake interrupt mark) set 1, unable to clear 0 phenomenon.

Solution:

Method 1: Software configuration brake signal is normal input IO interrupt, do not use BIF and brake interrupt. Method 2: Set 1 in the BIF to soft-reset TIM.

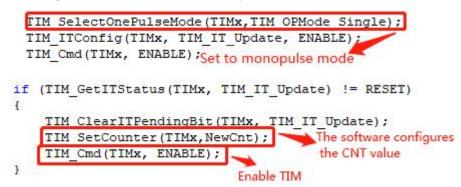

3.3.2 Precautions for software CNT value modification

Problem description:

In some cases, after the software changes the CNT value, TIM does not count the CNT reconfigured.

Case 1:

- > TIM is configured in monopulse mode with update interrupt enabled.

- > Modify the CNT value in interrupt and enable TIM.

# Attention:

In monopulse mode, the TIM counters of the SXX32F103 and MH2103C automatically stop when the next update event UEV is generated.

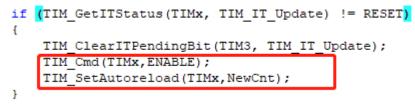

Case 2:

- > TIM is not configured with monopulse mode.

- In interrupt, the software disables TIM, changes the CNT value, and enables TIM again.

```

void TIM3_IRQHandler(void)

{

if (TIM_GetITStatus(TIMx, TIM_IT_Update) != RESET)

{

TIM_Cmd(TIMx, DISABLE);

TIM_ClearITPendingBit(TIM3, TIM_IT_Update);

TIM_SetCounter(TIMx, 1999);

TIM_Cmd(TIMx, ENABLE);

}

}

```

# Root cause:

The software modification CNT takes effect only when CEN is enabled.

# Solution:

If the monopulse mode is configured, after the update event is generated; To manually change the CNT value, enable TIM first.

➢ If the monopulse mode is not configured, you need to manually modify the CNT value and do not need to turn off TIM.

### 3.3.3 TIMDMABurst function use precautions

### Problem description:

When the Advanced & General TIM configures DBL to be non-O, a DMA request is generated, and DMA carries data only once.

| 15       | 14 | 13 | 12 | 11       | 10 | 9  | 8        | 7 | 6 | 5        | 4  | 3  | 2  | 1  | 0 |  |

|----------|----|----|----|----------|----|----|----------|---|---|----------|----|----|----|----|---|--|

| Reserved |    |    |    | DBL[4:0] |    |    | Reserved |   |   | DBA[4:0] |    |    |    |    |   |  |

|          |    | rw | rw | rw       | rw | rw |          |   |   | rw       | rw | rw | rw | rw |   |  |

Bits 15:13 Reserved, must be kept at reset value.

#### Bits 12:8 DBL[4:0]: DMA burst length

This 5-bit vector defines the number of DMA transfers (the timer recognizes a burst transfer when a read or a write access is done to the TIMx\_DMAR address). 00000: 1 transfer, 00001: 2 transfers, 00010: 3 transfers, ...

10001: 18 transfers.

Bits 7:5 Reserved, must be kept at reset value.

Bits 4:0 DBA[4:0]: DMA base address

This 5-bit vector defines the base-address for DMA transfers (when read/write access are done through the TIMx\_DMAR address). DBA is defined as an offset starting from the address of the TIMx\_CR1 register. Example: 00000: TIMx\_CR1, 00001: TIMx\_CR2, 00010: TIMx\_SMCR,

### Root cause:

The function mechanism of TIMDMABurst is different from SXX32F103.

### For SXX32F103:

When the Advanced & General TIM configures DBL to non-O, a DMA request is generated and DMA carries (DBL+1) data

### For MH2103C:

When the Advanced & General TIM configures DBL to non-O, a DMA request is generated and DMA carries (DBL+1) data

# Sol ution:

The software can configure TIM to send different DMA request signals to different DMA channels at the same time,

and each DMA channel carries a data to achieve the TIMDMABurst effect of SXX32F103.

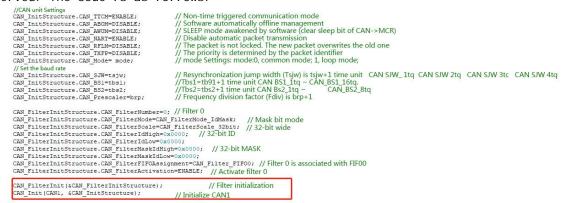

# 3.4 CAN module

# 3.4.1 Precautions for configuring a filter in hibernation mode Problem description:

The CAN module first initializes the filter and then initializes the controller, resulting in the phenomenon that data can be sent but cannot be received. The code is as follows:

# Root cause:

When configuring the CAN filter for the MH2103C, ensure that the CAN is in non-sleep mode.

### Solution:

To solve this problem, initialize the CAN controller and then configure the filter.

| //can单元设置                                 |                                                                              |

|-------------------------------------------|------------------------------------------------------------------------------|

| CAN_InitStructure.CAN_TTCM=DISABLE;       | //非时间触发通信模式                                                                  |

| CAN_InitStructure.CAN_ABOM=DISABLE;       | //软件自动离线管理                                                                   |

| CAN_InitStructure.CAN_AWUM=DISABLE;       | //睡眠模式通过软件唤醒(清除CAN->MCR的SLEEP位)                                              |

| CAN_InitStructure.CAN_NART=ENABLE;        | //禁止报文自动传送                                                                   |

| CAN_InitStructure.CAN_RFLM=DISABLE;       | //报文不锁定,新的覆盖旧的                                                               |

| CAN_InitStructure.CAN_TXFP=DISABLE;       | //优先级由报文标识符决定                                                                |

| CAN_InitStructure.CAN_Mode= mode;         | //模式设置: mode:0,普通模式;1,回环模式;                                                  |

| //设置波特率                                   |                                                                              |

| CAN_InitStructure.CAN_SJW=tsjw;           | //重新同步跳跃宽度(Tsjw)为tsjw+1个时间单位 CAN_SJW_1tq CAN_SJW_2tq CAN_SJW_3tq CAN_SJW_4tq |

| CAN_InitStructure.CAN_BS1=tbs1;           | //Tbs1=tbs1+1个时间单位CAN_BS1_1tq ~CAN_BS1_16tq                                  |

| CAN_InitStructure.CAN_BS2=tbs2;           | //Tbs2=tbs2+1个时间单位CAN_BS2_ltq ~ CAN_BS2_8tq                                  |

| CAN InitStructure.CAN Prescaler=brp;      | //分频系数(Fdiv)为brp+1                                                           |

| CAN Init(CAN1, &CAN InitStructure);       | //初始化can1                                                                    |

|                                           |                                                                              |

| CAN_FilterInitStructure.CAN_FilterNumber= |                                                                              |

| CAN_FilterInitStructure.CAN_FilterMode=CA |                                                                              |

| CAN_FilterInitStructure.CAN_FilterScale=C | AN_FilterScale_32bit; //32位宽                                                 |

| CAN_FilterInitStructure.CAN_FilterIdHigh= | 0x0000; //32位ID                                                              |

| CAN_FilterInitStructure.CAN_FilterIdLow=0 | ×0000;                                                                       |

| CAN_FilterInitStructure.CAN_FilterMaskIdH | igh=0x0000;//32位MASK                                                         |

| CAN_FilterInitStructure.CAN_FilterMaskIdL |                                                                              |

|                                           | ignment=CAN_Filter_FIF00;//过滤器0关联到FIF00                                      |

| CAN_FilterInitStructure.CAN_FilterActivat | ion=ENABLE;//激活过滤器0                                                          |

|                                           |                                                                              |

| CAN_FilterInit(&CAN_FilterInitStructure); | //滤波器初始化                                                                     |

|                                           |                                                                              |

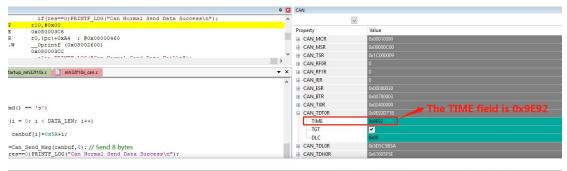

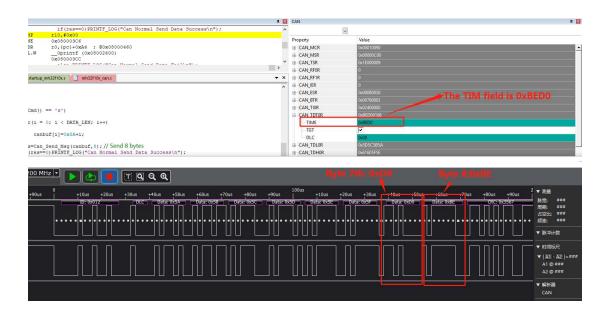

3.4.2 Send time stamp precautions

## Problem description:

Due to the different design, MH2103C uses CAN to send the timestamp, and the TIME[15:0] field in the CAN\_TDTxR register is different from that in SXX32F103 to fill the message location.

# For SXX32F103:

TIME[7:0] as the seventh byte and TIME[15:8] as the eighth byte replace the data written to CAN\_TDHxR[31:16] (DATA6[7:0] and DATA7[7:0]).

| Bit 31:16 | TIME[15:0]: Message time stamp<br>This field contains the value of the 16-bit timer at the time the packet is sent.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 15:9  | Reserved bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Bit 8     | TGT: Transmit global time<br>This bit is only valid if CAN is in time-triggered communication mode, i.e. the<br>TTCM bit of the CAN_MCR register is '1'.<br>0: does not send timestamp TIME[15:0];<br>1: Send timestamp TIME[15:0]. In a packet of length 8, the timestamp TIME[1 5:0] is<br>the last two bytes sent:<br>TIME[7:0] as the seventh byte and TIME[15:8] as the eighth byte replace the data written<br>to CAN_TDHXR [31:16] (DATA6[7:0] and DATA7[7:0]). In order to send out 2 bytes of the<br>timestamp, the DIC must be programmed to 8. |

| Bit 7:4   | Reserve the bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Bit 3:0   | DLC[15:0]: Send Data length code<br>This field specifies the data length of the data message or the data length of the<br>remote frame request. A message contains 0 to 8 bytes of data, which is determined<br>by the DLC.                                                                                                                                                                                                                                                                                                                               |

| 00 MHz | •••   |              |       |       | ବ୍ଭ   | ]     |          |       |           |         |       |            |       |        |       |                                                                                                                 |      |   |       |          |       |   |

|--------|-------|--------------|-------|-------|-------|-------|----------|-------|-----------|---------|-------|------------|-------|--------|-------|-----------------------------------------------------------------------------------------------------------------|------|---|-------|----------|-------|---|

| 90us   | 0<br> |              | +20us | +30us | +40us | +50us | +60us    | +70us | +80us     | +90us   | 100us | +10us      | +20us | +30us  | +40us | and the owner where the owner w |      |   | +70us | +80us    | +90us | 2 |

|        | ]     | <br>D: 0x012 |       |       |       |       | Data: 0x | ΠΠ    | ata: 0x5C | Data: ( |       | Data: 0x5E | Data  | : 0x5F |       | : 0x9E                                                                                                          | Data | П |       | CRC: 0x3 |       |   |

|        | L     |              |       |       |       |       |          |       |           |         |       |            |       |        |       |                                                                                                                 |      |   |       |          |       | Ü |

|        |       |              |       |       |       |       |          |       |           |         |       |            |       |        |       |                                                                                                                 |      |   |       |          |       |   |

# For MH2103C:

TIME[7:0] as the eighth byte and TIME[15:8] as the seventh byte replace the data written to CAN\_TDHxR[31:16] (DATA6[7:0] and DATA7[7:0]).

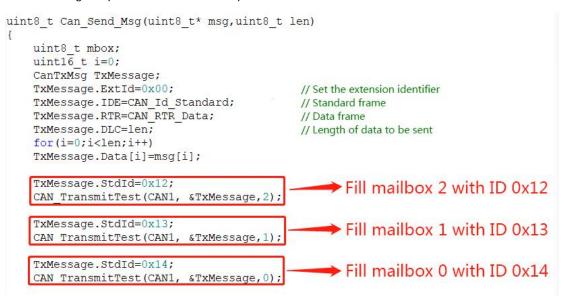

3.4.3 When TXFP is 1, the FIFO priority is different

# Problem description:

Due to different designs, the TXFP is set to 1 for the MH2103C. When multiple packets are waiting to be sent, the priority of sending packets is different from that of the SXX32F103.

The initial CAN configuration is as follows:

| <pre>//CAN unit Settings<br/>CAN_InitStructure.CAN_TTCM=DISABLE;<br/>CAN_InitStructure.CAN_ABOM=DISABLE;<br/>CAN_InitStructure.CAN_AWUM=DISABLE;<br/>CAN_InitStructure.CAN_NART=ENABLE;<br/>CAN_InitStructure.CAN_RFLM=DISABLE;<br/>CAN_InitStructure.CAN_Mode=_mode;</pre> | // Non-time triggered communication mode<br>// Software automatically offline management<br>// SLEEP mode awakened by software (clear sleep bit of CAN- >MCR)<br>// Disable automatic packet transmission<br>// The packet is not locked. The new packet overwrites the old one<br>. // mode Settings: mode:0, common mode; 1, loop mode; |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>// Set the baud rate<br/>CAN_InitStructure.CAN_SJW=tsjw;<br/>CAN_InitStructure.CAN_BS1=tbs1;<br/>CAN_InitStructure.CAN_BS2=tbs2;<br/>CAN_InitStructure.CAN_Prescaler=brp;<br/>CAN_Init(CAN1, &amp;CAN_InitStructure);</pre>                                            | The TXFP configuration is set to 1                                                                                                                                                                                                                                                                                                        |

The interface for sending packets can be defined as follows:

```

void CAN_TransmitTest (CAN_TypeDef* CANx, CanTxMsg* TxMessage,uint8_t TxMailbox)

1{

uint8 t transmit mailbox = 0;

transmit_mailbox = TxMailbox;

Email address

CANx->sTxMailBox[transmit_mailbox].TIR &= 1;

if (TxMessage->IDE == CAN Id Standard)

{

CANx->sTxMailBox[transmit mailbox].TIR |= ((TxMessage->StdId << 21) | \

TxMessage->RTR);

}

else

{

CANx->sTxMailBox[transmit mailbox].TIR |= ((TxMessage->ExtId << 3) | \

TxMessage->IDE | \

TxMessage->RTR);

}

TxMessage->DLC &= (uint8_t) 0x000000F;

CANx->sTxMailBox[transmit_mailbox].TDTR &= (uint32_t)0xFFFFFFF0;

CANx->sTxMailBox[transmit mailbox].TDTR |= TxMessage->DLC;

CANx->sTxMailBox[transmit_mailbox].TDLR = (((uint32_t)TxMessage->Data[3] << 24) |

((uint32 t)TxMessage->Data[2] << 16) |

((uint32 t)TxMessage->Data[1] << 8) |

((uint32_t)TxMessage->Data[0]));

CANx->sTxMailBox[transmit_mailbox].TDHR = (((uint32_t)TxMessage->Data[7] << 24) |

((uint32_t)TxMessage->Data[6] << 16) |

((uint32_t)TxMessage->Data[5] << 8) |

((uint32_t)TxMessage->Data[4]));

CANx->sTxMailBox[transmit_mailbox].TIR |= 1;

1

```

The filling sequence of the sent packets is as follows:

CAN packets are actually sent

#### For SXX32F103:

а.

11-

If the TXFP value is 1 and multiple packets are to be sent, the order of sending packets is determined by the order of requests.

| Bit 2 | <ul> <li>TXFP: Transmit FIFO priority</li> <li>When multiple packets are waiting to be sent at the same time, this bit determines the order in which these packets are sent.</li> <li>0: The priority is determined by the packet identifier.</li> <li>1: Priority is determined by the order in which requests are sent.</li> </ul> |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAN channel | Transmission direction | ID number  | Frame type | Frame format      | Length | Data                         |

|-------------|------------------------|------------|------------|-------------------|--------|------------------------------|

| ch1         | receive                | 0x0012     | Data frame | Standard<br>frame | 0x08   | x   5A 5B 5C 5D 5E 5F 60 61  |

| ch1         | receive                | 0x0013     | Data frame | Standard<br>frame | 0x08   | x   5A 5B 5C 5D 5E 5F 60 61  |

| ch1         | receive                | 0x0014     | Data frame | Standard<br>frame | 0x08   | x   5A 5B 5C 5D 5E 5F 60 61  |

| For MH210   | D3C:                   |            |            |                   |        |                              |

| When the    | TXFP va                | lue is 1 a | and multi  | ple pacl          | kets a | are to be sent, the order of |

| sending p   | backets                | is determi | ned by t   | he prio           | rity ( | of the mailbox number. Email |

priority: Email O> Email 1> Email 2.

The sequence of messages is as follows:

The sequence of messages is as follows:

| CAN channel | Transmission<br>direction | ID number | Frame type | Frame format      | t Length | Data                        |

|-------------|---------------------------|-----------|------------|-------------------|----------|-----------------------------|

| chi         | receive                   | 0x0012    | Data frame | Standard<br>frame | 0x08     | x   5A 5B 5C 5D 5E 5F 60 61 |

| chi         | receive                   | 0x0014    | Data frame | Standard<br>frame | 0x08     | x   5A 5B 5C 5D 5E 5F 60 61 |

| ch1         | receive                   | 0x0013    | Data frame | Standard<br>frame | 0x08     | x   5A 5B 5C 5D 5E 5F 60 61 |

# 3.5 FLASH module

### 3.5.1 Precautions for invoking the FLASH\_EraseOptionBytes() interface

# Problem description:

When the program uses the FLASH\_EraseOptionBytes() interface to erase the option byte area, there is a probability that the HardFault\_Handler exception will be interrupted.

# Solution:

MH2103C Modifies the FLASH\_EraseOptionBytes() interface as follows

Replace the following instructions with the SetStrt() interface

FLASH->CR |= CR\_OPTER\_Set;

FLASH->CR |= CR STRT Set;

FLASH\_WaitForLastOperation(EraseTimeout);

```

FLASH_Status FLASH_EraseOptionBytes(void)

1

uintl6_t rdptmp = RDP_Key;

FLASH Status status = FLASH COMPLETE;

/* Get the actual read protection Option Byte value */

if(FLASH GetReadOutProtectionStatus() != RESET)

-{

rdptmp = 0x00;

}

/* Wait for last operation to be completed */

status = FLASH WaitForLastOperation(EraseTimeout);

if (status == FLASH COMPLETE)

-{

/* Authorize the small information block programming */

FLASH->OPTKEYR = FLASH KEY1;

FLASH->OPTKEYR = FLASH KEY2;

/* if the previous operation is completed, proceed to erase the option bytes */

FLASH->CR |= CR OPTER Set;

FLASH->CR |= CR_STRT_Set;

/* Wait for last operation to be completed */

status = FLASH WaitForLastOperation(EraseTimeout);

SetStrt();

if(status == FLASH_COMPLETE)

{

/\ast if the erase operation is completed, disable the OPTER Bit \ast/

FLASH->CR &= CR_OPTER_Reset;

/* Enable the Option Bytes Programming operation */

FLASH->CR |= CR OPTPG Set;

/* Restore the last read protection Option Byte value */

OB->RDP = (uintl6_t)rdptmp;

/* Wait for last operation to be completed */

status = FLASH_WaitForLastOperation(ProgramTimeout);

if(status != FLASH TIMEOUT)

{

/\,^{\star} if the program operation is completed, disable the OPTPG Bit \,^{\star}/

FLASH->CR &= CR OPTPG Reset;

}

}

else

```

The SetStrt() interface is shown in the following figure, which is implemented in mh32f10x\_flash.c.

```

#if defined( CC_ARM)

__ASM_void SetStrt(void)

{

MOV

RO, PC

LDR

R1, [R0,#16]

R1, [R0,#32]

LDR

LDR

R0, =0x40022010

R1, =0x60

LDR

STR

R1,[R0]

NOP

NOP

NOP

NOP

NOP

NOP

FLAGLABLE

R1, =0x4002200C

LDR

LDR

R2, [R1]

AND

R2, #0x01

CMP

R2, #0x00

BNE

FLAGLABLE

ΒX

lr

}

#elif defined(__ICCARM__)

void SetStrt(void)

{

ASM ("MOV

RO, PC\n"

"LDR

R1, [R0,#16]\n"

"LDR

R1, [R0,#32]\n"

"LDR

R0, =0x40022010\n"

"LDR

R1, =0x60\n"

"STR

R1, [R0]\n"

"NOP\n"

"NOP\n"

"NOP\n"

"NOP\n"

"NOP\n"

"NOP\n"

"FLAGLABLE:\n"

"LDR R1, =0x4002200C\n"

R2, [R1]\n"

"LDR

R2, R2, #0x01\n"

"AND

"CMP

R2, #0x00\n"

"BNE

FLAGLABLE\n"

"BX

lr");

}

#elif defined(__GNUC__)

void SetStrt(void)

{

asm("MOV

R0, PC");

asm("LDR

R1, [R0,#16]");

R1, [R0,#32]");

asm("LDR

```

# 3.6 USART modul e

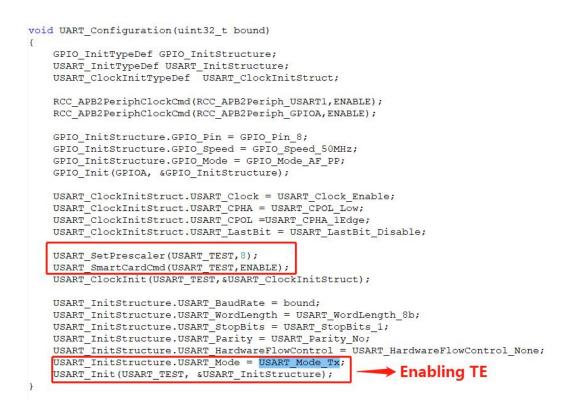

3.6.1 Precautions for clock output in smart card mode

# Problem description:

```

When only CLK is configured in smart card mode, there is no clock output. The

configuration is as follows:

void UART_Configuration(uint32_t bound)

{

GPIO InitTypeDef GPIO InitStructure;

USART_InitTypeDef USART_InitStructure;

USART_ClockInitTypeDef USART_ClockInitStruct;

RCC APB2PeriphClockCmd(RCC APB2Periph USART1, ENABLE);

RCC APB2PeriphClockCmd (RCC APB2Periph GPIOA, ENABLE);

GPIO InitStructure.GPIO Pin = GPIO Pin 8;

GPIO InitStructure.GPIO Speed = GPIO Speed 50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO Init (GPIOA, & GPIO InitStructure);

USART ClockInitStruct.USART Clock = USART Clock Enable;

USART ClockInitStruct.USART CPHA = USART CPOL Low;

USART ClockInitStruct.USART CPOL =USART CPHA 1Edge;

USART ClockInitStruct.USART LastBit = USART LastBit Disable;

Configure clock frequency division.

USART SetPrescaler(USART TEST,8);

The smartcard mode was

USART SmartCardCmd(USART TEST, ENABLE); .

enabled

USART ClockInit(USART TEST, &USART ClockInitStruct);

```

}

#### Root cause:

The clock output condition of the MH2103CUSART smart card mode is different from that of the SXX32F103, and is also controlled by the send enable TE.

### Sol ution:

After the clock frequency division is configured and the smart card

mode is enabled, set the transmit TE function to 1.

As shown in the picture below:

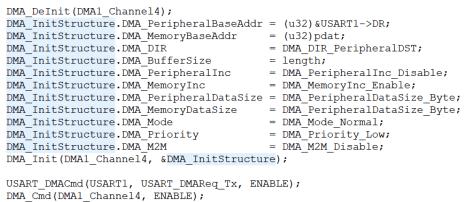

# 3.6.2 When DMA is used to send data, USARTTC flags are used to determine whether all data is sent. Precautions

#### Problem description:

When DMA is used to send data larger than 2Byte, the USARTTC flag is used

to confirm whether the data is sent. You Need to proceed,

for example:

USART1 is configured normally, and RE and TE are enabled. As shown in the following picture

```

RCC_APB2PeriphClockCmd(RCC_APB2Periph_USART1,ENABLE);

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA,ENABLE);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_9;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO_Init(GPIOA, &GPIO_InitStructure);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_10;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING;

GPIO_Init(GPIOA, &GPIO_InitStructure);

USART_InitStructure.USART_BaudRate = bound;

USART_InitStructure.USART_WordLength = USART_WordLength_8b;

USART_InitStructure.USART_StopBits = USART_StopBits_1;

USART_InitStructure.USART_Parity = USART_Parity_No;

USART_InitStructure.USART_HardwareFlowControl = USART_HardwareFlowControl_None;

USART_InitStructure.USART_Mode = USART_Mode_Rx | USART_Mode_Tx;

USART_Init(USART1, &USART_InitStructure);

```

```

USART_Cmd(USART1, ENABLE);

```

Configure and enable the DMA channel to carry data. As shown in the following picture

> After DMATC is set, determine the USARTTC flag. As shown in the following picture

```

while(DMA_GetFlagStatus(DMA1_FLAG_TC4) != SET);

while(USART GetFlagStatus(USART1, USART FLAG TC) != SET);

```

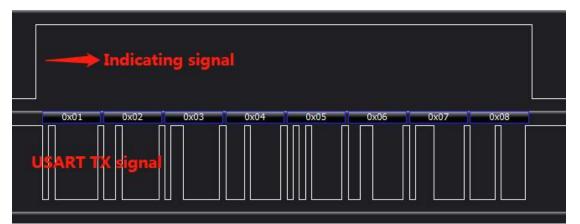

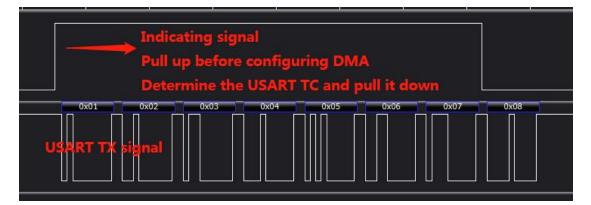

Detect indicating signals and data sent by USARTTX pins. As shown in the following picture

For SXX32F103:

For MH2103C:

# Sol ution:

Before configuring DMA, disable TE. After DMA is configured, TE is enabled to send data. As shown in the following picture

| USART1->CR1 &= ~BIT(3);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | e TE                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA_DeInit(DMA1_Channel4);<br>DMA_InitStructure.DMA_PeripheralBaseAddr<br>DMA_InitStructure.DMA_MemoryBaseAddr<br>DMA_InitStructure.DMA_DIR<br>DMA_InitStructure.DMA_BufferSize<br>DMA_InitStructure.DMA_PeripheralInc<br>DMA_InitStructure.DMA_MemoryInc<br>DMA_InitStructure.DMA_PeripheralDataSize<br>DMA_InitStructure.DMA_MemoryDataSize<br>DMA_InitStructure.DMA_MemoryDataSize<br>DMA_InitStructure.DMA_MemoryDataSize<br>DMA_InitStructure.DMA_Mode<br>DMA_InitStructure.DMA_Priority<br>DMA_InitStructure.DMA_M2M | <pre>= (u32)pdat;<br/>= DMA_DIR_PeripheralDST;<br/>= length;<br/>= DMA_PeripheralInc_Disable;<br/>= DMA_MemoryInc_Enable;<br/>= DMA_PeripheralDataSize_Byte;<br/>= DMA_PeripheralDataSize_Byte;<br/>= DMA_Mode_Normal;<br/>= DMA_Priority_Low;<br/>= DMA_M2M_Disable;</pre> |

| USART_DMACmd(USART1, USART_DMAReq_Tx, END<br>DMA_Cmd(DMA1_Channel4, ENABLE);<br>USART1->CR1  = BIT(3); Enable T                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                             |

## 3.6.3 Smart card & Single-wire half-duplex mode TX pin configuration precautions

### Problem description:

In smart card & single-wire half-duplex mode, when the TX pin is configured to multiplexed open-leak mode, the TX output is always low. The I/O mode is configured as follows:

```

GPIO InitStructure.GPIO Mode = GPIO Mode AF OD;

```

### Root cause:

Due to the different design, the smart card & single-wire half-duplex mode of the MH2103CUSART requires the TX pin to be configured as a multiplexed push-pull mode.

# Sol uti on:

In smart card & single-wire half-duplex mode, the TX pin is configured as the push-pull mode, which can be used normally. The I/O mode is configured as follows:

GPIO InitStructure.GPIO Mode = GPIO Mode AF PP;

### 3.6.4 Precautions for DR Overflow when accepting data

# Problem description:

When RXNE is set to 1, it is not reset (DR Is not read), and one or more

characters are received, RXNE is abnormal.

#### Root cause:

The design is different.

# Sol ution:

Software is designed to avoid DR Overflow. You can use the following methods:

- Use interrupt /DAM mode to obtain data to ensure that the DR Can be

- read in time after RXNE is set.

- > When the RXNE reads data, ensure that the CPU detects the RXNE status in real time when the data is received.

# 3.7 SPI module

3.7.1 As the Master, this section describes the precautions for sending and receiving data

#### in full-duplex mode

#### Problem description:

When communicating with SPI as Master, the received data is abnormal.

For example:

The SPI is configured in Master two-wire full-duplex mode. As shown in the following picture

```

SPI_InitStructure.SPI_Direction = SPI_Direction_2Lines_FullDuplex;

SPI_InitStructure.SPI_Mode = SPI_Mode_Master;

SPI_InitStructure.SPI_DataSize = SPI_DataSize_8b;

SPI_InitStructure.SPI_CPOL = SPI_CPOL_High;

SPI_InitStructure.SPI_CPHA = SPI_CPHA_2Edge;

SPI_InitStructure.SPI_NSS = SPI_NSS_Soft;

SPI_InitStructure.SPI_BaudRatePrescaler = SPI_BaudRatePrescaler_256;

SPI_InitStructure.SPI_FirstBit = SPI_FirstBit_MSB;

SPI_InitStructure.SPI_CRCPolynomial = 7;

SPI_Init(SPIx, &SPI_InitStructure);

```

Send and receive data according to the following figure.

```

// Send Data0, Data1; Do not operate to receive DR

SPI_I2S_SendData(SPIx, Data0);

while (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_TXE) == RESET);

while (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_BSY) == RESET);

SPI_I2S_SendData(SPIx, Data1);

while (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_TXE) == RESET);

while (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_BSY) == RESET);

```

```

// Read the DR Once to clear the previously received data

while (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_RXNE) == RESET);

SPI_I2S_ReceiveData(SPIx);

```

```

// Send data Data2; And read DR, get the received data receive|

SPI_I2S_SendData(SPIx, Data2);

while (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_TXE) == RESET);

while (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_BSY) == RESET);

while (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_RXNE) == RESET);

receive = SPI_I2S_ReceiveData(SPIx);

```

MH2103C sends Data2 The received data is abnormal data.

### Root cause:

The MH2103CSPI has a 16Byte receiving FIFO. The data received by Data1 is cached in the receiving FIFO, and the operation of reading the DR Once does not clear all the useless data in the FIFO, resulting in the data received by the subsequent sending Data2 is not the expected data.

#### Sol ution:

As a Master, the DR Is read every time the data is sent, ensuring that no residual data in the FIFO can be resolved. As shown in the picture below:

```

// Send Data 0, Data 1; The DR Is read once after each data transmission

SPI_I2S_SendData(SPIx, Data0);

while (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_TXE) == RESET);

while (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_BSY) == RESET);

while (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_RXNE) == RESET);

SPI_I2S_ReceiveData(SPIx);

```

```

SPI_I2S_SendData(SPIx, Datal);

while (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_TXE) == RESET);

while (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_BSY) == RESET);

while (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_RXNE) == RESET);

SPI_I2S_ReceiveData(SPIx);

```

```

// Send Data 2; And read the DR To get the received data receive

SPI_I2S_SendData(SPIx, Data2);

while (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_TXE) == RESET);

while (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_BSY) == RESET);

while (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_RXNE) == RESET);

receive = SPI_I2S_ReceiveData(SPIx);

```

#### 3.7.2 Turn off the SPE in BUSY state

#### Problem description:

When the SPI is operated, if the software does not determine the non-busy status of the SPE when it is turned off, data may fail to be sent and received. Operation as shown below:

The MH2103C can normally send 0xAA, but cannot send 0x55.

```

SPI_I2S_SendData(SPI1, 0xAA);

while(SPI_I2S_GetFlagStatus(SPI1, SPI_I2S_FLAG_BSY) == RESET);

SPI_Cmd(SPI1, DISABLE);

SPI_Cmd(SPI1, ENABLE);

while(SPI_I2S_GetFlagStatus(SPI1, SPI_I2S_FLAG_TXE) == RESET);

SPI_I2S_SendData(SPI1, 0x55);

```

Root cause:

MH2103CSPI When the SPE device is in BUSY state, disabling the SPE device takes effect after data sending is complete (in non-busy state). Ignoring the enabling action does not take effect.

# Sol ution:

Before shutting down the SPE, check whether the SPE is in BUSY state.

You can shut down the SPE only when the SPE is not BUSY.

#### 3.7.3 Precautions for Data Transmission Using DMA

#### Problem description:

When the SPI uses DMA to transmit data, the data received is incorrect.

### Sol ution:

When SPI uses DMA to transmit data, it is recommended that peripheral DAM

and DMA channel be enabled/disabled at the same time. As shown in the picture below:

DMA\_Cmd(FLASH\_SPI\_RX\_DMA\_CHANNEL, ENABLE); DMA\_Cmd(FLASH\_SPI\_TX\_DMA\_CHANNEL, ENABLE); SPI\_I2S\_DMACmd(FLASH\_SPI\_MASTER, SPI\_I2S\_DMAReq\_Tx, ENABLE); SPI\_I2S\_DMACmd(FLASH\_SPI\_MASTER, SPI\_I2S\_DMAReq\_Rx, ENABLE);

SPI\_I2S\_DMACmd(FLASH\_SPI\_MASTER, SPI\_I2S\_DMAReq\_Tx, DISABLE); SPI\_I2S\_DMACmd(FLASH\_SPI\_MASTER, SPI\_I2S\_DMAReq\_Rx, DISABLE); DMA\_Cmd(FLASH\_SPI\_TX\_DMA\_CHANNEL, DISABLE); DMA\_Cmd(FLASH\_SPI\_RX\_DMA\_CHANNEL, DISABLE);

# 3.8 USB module

#### 3.8.1 USB use precautions

#### Problem description:

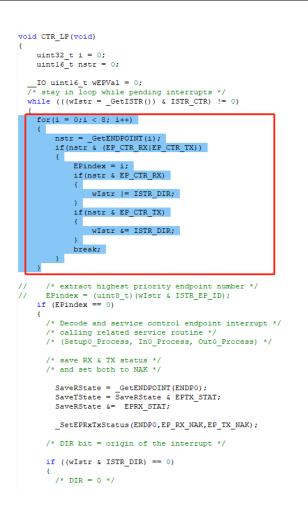

When USB is configured in Slave mode, the Host sends requests from different endpoints or from the same endpoint in different directions in a short period of time, and there is a probability of crash.

#### Root cause:

The EP\_ID and DIR update mechanism in the USB\_ISTR(Interrupt status

register) of the MH2103C USB is different from that of the SXX32F103.

### Solution:

Modify the CTR\_LP() interface, as shown in the following figure. After modification, it is compatible with SXX32F103.

# 3.9 DMA module

# 3.9.1 DMA usage precautions

#### Problem description:

When data is being transferred by a Channel in the DMA module, modifying the

CNT value (data transfer quantity) of another Channel may not take effect.

# Root cause:

The CNT(Data Transfer quantity) modification of MH2103CDMAChannel takes effect under different conditions from SXX32F103.

### Solution:

The software prevents the DMA Channel from modifying the CNT value (the amount of data transferred) of another Channel while it is moving data.

# 3.10 IIC module

# 3.10.1 Send start bit & Stop bit as Master Note

# Problem description:

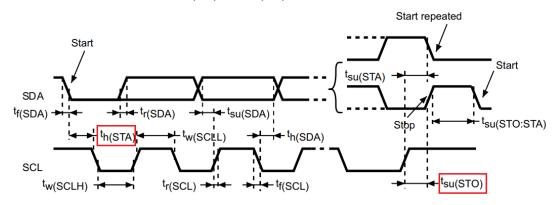

As shown in the figure below MH2103C start bit Hold time  $(t_{h(STA)})$  & stop bit Hold time  $(t_{SU(STO)})$  and SXX32F103 is different.

When the peer end is an I/O analog Slave, you need to confirm whether the peer end has requirements for  $t_{h(STA)}$  and  $t_{SU(STO)}$ .

# For SXX32F103:

$t_{h(STA)}$  and  $t_{SU(STO)}$  equal the high level time of the SCL.

# For MH2103C:

In standard mode,  $t_{h(STA)} \& t_{SU(STO)}$  equals (FREQ\*4+8) $*T_{APB1^{\circ}}$  In fast mode,  $t_{h(STA)} \& t_S$

U(STO) equals (FREQ+8)  $*T_{APB1}$  °

### Root cause:

Different design.

# Sol uti on:

If you have requirements for  $t_{h(STA)}$  and  $t_{SU(STO)}$  time, you can adjust the time by modifying FREQ or modifying APBICLK.

# 4. ISP, emulator, offline burner use precautions

# 4.1 ISP tool usage Precautions

MH2103C supports the ISP tools commonly used in the market.

The programmer includes STMFlashLoader, FlyMcu, and STM32CubeProgrammer.

# STMF1ashLoader:

| 🧼 Flash Load                  | der Demonstr     | _               | _                 | □ X         |

|-------------------------------|------------------|-----------------|-------------------|-------------|

|                               |                  | life.au         | gmented           |             |

| Select the cor<br>connection. | mmunication port | and set setting | gs, then click ne | ext to open |

| Common for                    | all families     |                 |                   |             |

| UART                          |                  |                 |                   |             |

| Port Name                     | COM8             | ▼ Parity        | y Even            | •           |

| Baud Rate                     | 115200           | 💌 Echo          | ) Disat           | oled 💌      |

| Data Bits                     | 8                | - Time          | out(s) 10         | •           |

|                               |                  |                 |                   |             |

|                               |                  |                 |                   |             |

|                               |                  |                 |                   |             |

|                               |                  |                 |                   |             |

|                               |                  |                 |                   |             |

|                               |                  |                 |                   |             |

|                               |                  |                 |                   |             |

|                               |                  |                 |                   |             |

|                               |                  |                 |                   |             |

|                               | Back             | Next            | Cancel            | Close       |

# FlyMcu:

| K机下载时的程P  | <u> </u>           |                              |             |           |              |  |  |

|-----------|--------------------|------------------------------|-------------|-----------|--------------|--|--|

|           |                    |                              |             |           | <br>☑编程前重装文件 |  |  |

| 戶持万用编程器   | STMISP             |                              | NXP ISP EP9 | 968_RS232 |              |  |  |

| 开始编       | 程 <mark>(P)</mark> | ✓校验<br>□编程后<br>□使用Ra<br>□连续情 |             |           |              |  |  |

| 读器件信息(R)  | 清院                 | 就片(Z)                        | 读FLASH      | ł         |              |  |  |

| 选项字节区:    |                    |                              |             |           |              |  |  |

| ]编程到FLASH | 时写选项;              | Z节                           |             |           |              |  |  |

| 设定选项字     | 节等                 |                              |             |           |              |  |  |

|           |                    |                              |             |           |              |  |  |

|           |                    |                              |             |           |              |  |  |

|           |                    |                              |             |           |              |  |  |

|           |                    |                              |             |           |              |  |  |

|           |                    |                              |             |           |              |  |  |

|           |                    |                              |             |           |              |  |  |

|           |                    |                              |             |           |              |  |  |

|           |                    |                              |             |           |              |  |  |

|           |                    |                              |             |           |              |  |  |

|           |                    |                              |             |           |              |  |  |

|           |                    |                              |             |           |              |  |  |

STM32CubeProgrammer:

| Pro STN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 132CubeProgrammer                                    |                                                                                                                 | - 🗆 X                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------|

| STM32<br>Cube                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Programmer 🚳                                         | F 🕨                                                                                                             | y 🛧 🏹                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Memory & File edition                                |                                                                                                                 | Not connected         |